EE618 CMOS模擬集成電路設計 從理論到實踐的集成電路設計探索

CMOS模擬集成電路設計是現(xiàn)代電子系統(tǒng)的核心,它承載著信號處理、電源管理、數(shù)據(jù)轉(zhuǎn)換等關(guān)鍵功能。EE618課程作為該領(lǐng)域的專業(yè)課程,旨在系統(tǒng)性地講解CMOS模擬集成電路的設計原理、方法與技術(shù),培養(yǎng)學生從理論分析到實際設計的綜合能力。

在集成電路設計中,CMOS技術(shù)因其低功耗、高集成度和良好的可擴展性而占據(jù)主導地位。模擬電路設計尤其挑戰(zhàn)性,因為它對噪聲、線性度、帶寬和功耗等參數(shù)極為敏感。EE618課程通常從MOSFET器件物理基礎(chǔ)講起,深入分析其小信號模型、頻率響應及非線性特性,為后續(xù)電路設計奠定堅實的理論基礎(chǔ)。

課程的核心內(nèi)容涵蓋基本放大器的設計,包括共源極、共柵極、共漏極(源極跟隨器)以及差分放大器。這些基礎(chǔ)模塊是構(gòu)成復雜模擬系統(tǒng),如運算放大器、比較器、基準電壓源和振蕩器的基石。通過深入理解這些模塊的增益、帶寬、輸入輸出阻抗和穩(wěn)定性,學生能夠逐步掌握如何優(yōu)化電路性能以滿足特定應用需求。

EE618還著重介紹模擬集成電路中的關(guān)鍵設計考慮,如偏置技術(shù)、頻率補償、噪聲分析和版圖設計。偏置電路確保晶體管工作在合適的區(qū)域,而頻率補償技術(shù)(如米勒補償)則用于防止放大器在反饋應用中發(fā)生振蕩。噪聲分析幫助設計師評估電路的信噪比,特別是在低信號應用中至關(guān)重要。版圖設計則涉及物理實現(xiàn)的細節(jié),包括匹配、寄生效應控制和可靠性問題,這些直接影響到電路的最終性能和成品率。

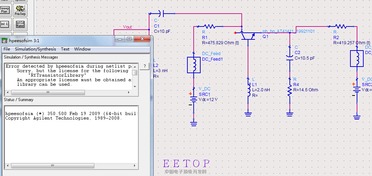

隨著技術(shù)的發(fā)展,課程也會涉及先進主題,如低壓設計、開關(guān)電容電路和數(shù)據(jù)轉(zhuǎn)換器(ADC/DAC)基礎(chǔ)。這些內(nèi)容反映了現(xiàn)代電子系統(tǒng)對高能效和高精度的追求。通過項目實踐和仿真工具(如Cadence或SPICE)的使用,學生能夠?qū)⒗碚撝R應用于實際設計,從電路原理圖繪制、仿真驗證到版圖實現(xiàn),完成完整的集成電路設計流程。

EE618 CMOS模擬集成電路設計課程不僅提供了深入的技術(shù)知識,還培養(yǎng)了解決復雜工程問題的能力。在集成電路日益復雜和集成的今天,掌握這些設計技能對于從事半導體行業(yè)或相關(guān)研究的學生至關(guān)重要,為他們在創(chuàng)新和開發(fā)下一代電子系統(tǒng)中打下堅實基礎(chǔ)。

如若轉(zhuǎn)載,請注明出處:http://www.xxyzz.cn/product/24.html

更新時間:2026-03-09 03:03:09